IDF 2015: Stromsparen mit Skylake

Mit Skylake geht es den althergebrachten Stromspartechniken SpeedStep und S3 (Suspend to RAM) an den Kragen. Damit das funktioniert, muss das Betriebssystem mitspielen.

Auf seiner Entwicklerkonferenz Intel Developer Forum (IDF) in San Francisco hat Intel Details zu den Stromsparfunktionen veröffentlicht, die die neue Prozessorgeneration Skylake [1] mit sich bringt. Manche davon laufen prozessorintern ab, andere erfordern hingegen die aktive Mitarbeit des Betriebssystems. Zu ersteren zählt das bereits bei der Enthüllung der Skylake-Architektur [2] angedeutete verfeinerte Abschalten (Power Gating) von Funktionseinheiten wie AVX oder die geringere Assoziativität des L2-Cache.

(Bild: Intel / IDF15)

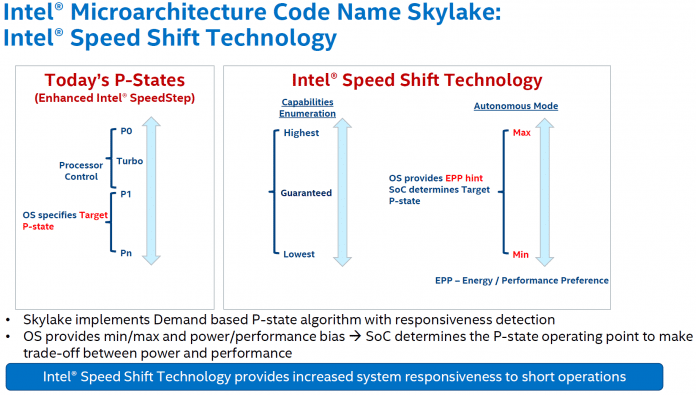

Viele neue Techniken ersetzen hingegen Altbekanntes: Speed Shift löst SpeedStep ab, Disconnected Standby ersetzt den Standby-Modus S3 alias Suspend to RAM. Damit das funktioniert, muss das Betriebssystem mitspielen – was laut Intel derzeit nur mit Windows 10 [3] funktioniert. Auch werden wohl nicht alle Skylakes alle Stromsparfunktionen bekommen: Hauptsächlich sind sie für die SoC-Varianten vorgesehen, also die Doppelkern-Ableger der Core-i- und Core-M-Schienen.

Technische Details zu den Stromsparfunktionen liefert der Hintergrundartikel auf c't online:

(mue [5])

URL dieses Artikels:

https://www.heise.de/-2785645

Links in diesem Artikel:

[1] http://www.heise.de/thema/skylake

[2] https://www.heise.de/news/IDF-2015-Intel-enthuellt-ein-wenig-die-Skylake-Architektur-2784862.html

[3] http://www.heise.de/thema/Windows-10

[4] https://www.heise.de/ratgeber/Neue-Stromsparfunktionen-von-Skylake-unter-Windows-10-2786026.html

[5] mailto:mue@ct.de

Copyright © 2015 Heise Medien